# **Optimization of the Radix 4 and Radix 8 Booth Algorithms and Their FPGA Realization**

Krutideepa Bhol, M.Durairaj, L.Saravanan, B.Kaleeswari, M.Renuga, K.Kannadasan

Department of ECE, PERI Institute of Technology, Chennai, India.

| Article Information                             |                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Received : 09 Jan 2023                          | <b>Abstract</b> — the multipliers play a vital role in performance of any electronics system. But the major drawback is it consumes more power and area. There are numerous methods and                                                                                                    |

| Revised : 22 Feb 2023                           | techniques available to improve performance while reducing power and space usage. The                                                                                                                                                                                                      |

| Accepted : 03 Mar 2023                          | primary goal of any algorithm for multiplying numbers is to reduce the partial product                                                                                                                                                                                                     |

| Published <u>19 Mar 2023</u>                    | summation. The booth method is one of the most popular and successful algorithms. In this paper, we propose and implement the booth algorithms for radix 4 and radix 8. In the multiplier encoding, the partial products of the radix 4 algorithm are reduced to $n/2$ , while the partial |

| <u>Corresponding Author:</u><br>Krutideepa Bhol | products of the radix 8 algorithm can be reduced to $n/3$ . The Xilinx Vivado tool is used to produce the simulation results.                                                                                                                                                              |

|                                                 | Keywords: Booth algorithm; Booth multiplier; encoding;                                                                                                                                                                                                                                     |

**Copyright** © **2023: Krutideepa Bhol,** This is an open access distribution, and reproduction in any medium, provided Access article distributed under the Creative Commons Attribution License the original work is properly cited License, which permits unrestricted use.

**Citation: Krutideepa Bhol, M.Durairaj, L.Saravanan, B.Kaleeswari, M.Renuga, K.Kannadasan**. "Optimization of the Radix 4 and Radix 8 Booth Algorithms and Their FPGA Realization", Journal of Science, Computing and Engineering Research, 6(3), 96-99, 2023.

# I. INTRODUCTION

HIGH performance processors are in high demand in today's industrial market. Arithmetic operations such as addition, multiplication, and subtraction are invoked in many digital circuits to improve processing speed [1-3]. The multiplier is the slowest part in the system, and its performance determines system performance. The multiplier also takes up a lot of space and has a lot of power dissipation, which affects the overall performance of the system. Multipliers are employed in a variety of applications, including digital signal processing, loss applications, artificial neural networks, machine learning, and many more [4-6].

We have several power reduction methods and multipliers to improve the multiplier's performance. Booth algorithm requires reduced processing time, less design space, and consumes extremely little power. However, the main issue is that the delay is greater. The multiplication operation consists of two major phases, which are as follows:

a. Partial products addition

b. Partial products generation

Multiplier speed can be enhanced by reducing partial products and increasing the speed of partial product summation [7-9].

We will provide optimized radix 4 and radix 8 booth methods for arithmetic operations in this research article.

# II. BOOTH ALGORITHM

The booth algorithm was developed by Andrew Donald Booth in year of 1950 at Birkbeck College in Bloomsbury, London. This algorithm was an investigation of computer architecture. Using the 2's complement notation, this booth algorithm multiplies two signed binary values. This algorithm was created while conducting crystallographic research. Less additions and subtraction can be seen in the booth algorithm. The Booth multiplier is the multiplier that does calculations more quickly [10–12]. ASIC products frequently use this booth algorithm because of its small size and quick processing time.

There are three main steps in the booth algorithm:

- a. Summation of partial products

- b. Reduction of partial products

- c. Generation of partial products

The production of partial products in the booth algorithm depends on the recoding process. The procedure makes use of the Booths recoding technique, which is based on the idea that partial products can be produced for a collection of 0s and 1s.

Recoding algorithms' primary goal is to provide effective Partial products. Usually, the Radix utilized for recoding determines whether there will be an increase in partial product [13–15]. Less power and space are provided by this recoding process. Available at https://jscer.org

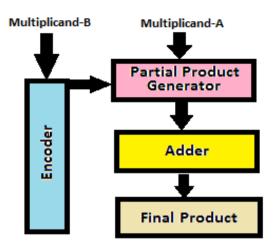

Fig. 1 illustrates the booth algorithm's block diagram, which multiplies two signed binary values in the form of a 2's complement.

We have four blocks in this algorithm, and they function as follows:

#### i. Encoder:

A digital circuit encoder executes a decoder's opposite operation. It features n outputs and 2n inputs. Here, we have used the encoder's multiplicand B as the input to the booth algorithm, and the encoder's partial product generator as the output. The encoder's output is a binary representation of the input value, and vice versa.

## ii. Partially Product Generator:

The partial product generator's primary goal is to make multiplication computations simpler. A group of 0s and 1s can yield the partial products. The speed of the summing of partial products is improved by the partial product reduction.

#### iii. Adder:

The next phase is summarizing partial products after producing and reducing partial products. To complete this step, we can employ a carry save adder or a carry look ahead adder. There are numerous additional alternatives, including parallel pre-fix adders like the Kogge Stone Adder, Wallace tree adders, compressor adders, and more. We can lower the delay parameter by carefully selecting an adder.

#### iv. Final product:

The output will be the multiplied 2's compliment number from the inputs multiplicand A and multiplicand B, which can be viewed as two signed binary values.

# (i) RADIX 4:

The multiplicands in radix 4 recoding are based on multiplier bits, and it compares three bits at a time using an overlapping process. The grouping will then begin from the LSB bit. Radix 4's primary benefit is its n/2 reduction in the number of partial products.

The steps for radix 4 are as follows:

a. Add 0 to the right of the LSB bit as the first step.

b. We can extend the sign bit 1 place when n is even.

c. The partial products are drawn from the set (-2, 2, 0, 1,-1) where each vector's value is contained.

| Y(i+1) | Y(i) | Y(i-1) | Mi | Operation on X |

|--------|------|--------|----|----------------|

| 0      | 0    | 0      | 0  | 0X             |

| 0      | 0    | 1      | +1 | +1X            |

| 0      | 1    | 0      | +1 | +1X            |

| 0      | 1    | 1      | +2 | +2X            |

| 1      | 0    | 0      | -2 | -2X            |

| 1      | 0    | 1      | -1 | -1X            |

| 1      | 1    | 0      | -1 | -1X            |

| 1      | 1    | 1      | 0  | 0X             |

Table 1: Booth Algorithm Radix 4 truth table

The booth encoding table for the Radix 4 booth algorithm is shown in Table 1. For an example, an 8X8 bit radix 4 considering signed bit as 0 and x as input data of 8-bit ; y as input data of 8-bit and k as the output data , x=111111111 y=11111111 then k = 1111111000000001

# (ii) RADIX 8:

The only difference between radix 8 booth recoding and radix 4 booth recoding is that we examine quartets of bits rather than triplets. In contrast to Radix 4, which decreases the number of partial products to n/2, Radix 8 reduces the number of partial products to n/3. This decrease in Partial products results in faster computations with less power and space consumption.

The booth encoding table for the Radix 8 booth algorithm is shown in Table 2.

| Multiplier Bits |   |   | Bits | <b>Operation on Multiplicand</b> |

|-----------------|---|---|------|----------------------------------|

| Α               | В | С | D    | X                                |

| 0               | 0 | 0 | 0    | 0X                               |

| 0               | 0 | 0 | 1    | +1X                              |

| 0               | 0 | 1 | 0    | +1X                              |

| 0               | 0 | 1 | 1    | +2X                              |

| 0               | 1 | 0 | 0    | +2X                              |

| 0               | 1 | 0 | 1    | + <b>3X</b>                      |

| 0               | 1 | 1 | 0    | +3X                              |

| 0               | 1 | 1 | 1    | +4X                              |

| 1               | 0 | 0 | 0    | -4X                              |

| 1               | 0 | 0 | 1    | -3X                              |

| 1               | 0 | 1 | 0    | -3X                              |

| 1               | 0 | 1 | 1    | -2X                              |

| 1               | 1 | 0 | 0    | -2X                              |

| 1               | 1 | 0 | 1    | -1X                              |

| 1               | 1 | 1 | 0    | -1X                              |

| 1               | 1 | 1 | 1    | 0X                               |

Table 2: Booth Algorithm Radix 8 truth table

For an example , an 8X8 bit radix 8 considering the signed bit as 1 and x as input data of 8-bit ; y as input data of 8-bit and k as the output data , x=11111111 y=11111111 then k = 111111111111111111

## Available at https://jscer.org

#### III. EXPERIMENTAL OBSERVATIONS

The investigational observations were carried out on Xilinx Vivado simulator. Verilog was used to write the HDL code, and vivado was used to display the results of the simulation. The Radix 4 and Radix 8 Booth algorithms' technology schematic, RTL schematic, and wave shapes are displayed here. As opposed to the radix 8 Booth method, which reduces the partial products by n/3 times, radix 4 reduces its partial products to half, or n/2 times.

# (i). Booth algorithm Radix 4 results

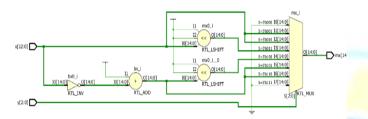

## (a) RTL schematic:

Figure 3 shows the RTL schematic of booth algorithm radix 4, where it provides the information regarding digital logic design in the form of symbols like multipliers, adders etc.

Fig 3: The RTL Schematic of booth algorithm Radix 4

# (b) Simulation Timing Diagram

|              |       | 1.184840 us                   |      |

|--------------|-------|-------------------------------|------|

| Name         | Value | 0 us  20 us  40 us  60 us  80 | us , |

| 🖬 📲 x[12:0]  | 2454  | 2#54                          |      |

| 🗄 📲 y[2:0]   | 0     |                               |      |

| 🖻 📲 mx[14:0] | 0     | 0 2454 4908 -4908 -2454 0     |      |

| 🖬 📲 x1[14:0] | 2454  | 2454                          |      |

| 🖬 📲 bx[14:0] | -2454 | -2454                         |      |

|              |       |                               |      |

|              |       |                               |      |

|              |       |                               |      |

Fig 4: Simulation Timing Diagram of Booth algorithm Radix 4

In this case, the input values for x and y is 12 bits each and has a range of 0 to 7; m is the output value. For instance, when y = 0 and 1 and x = 100110010110 (2454), the output m value remains the same, or "0." The operation is +1x for y = 1 and 2, resulting in m = 2454 as the output value. The procedure is +2x for y=3, resulting in a value of m = 4908.

# (i). Booth algorithm Radix 8 results

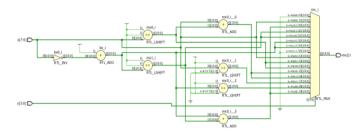

## (a) RTL schematic:

Figure 5 shows the RTL schematic of booth algorithm radix 8, where it provides the information regarding digital logic design in the form of symbols like multipliers, adders etc.

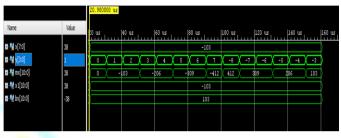

In this case, the output is "m" and the inputs "x" and "y" are each 4 bits wide and range from 0 to 15. If the input values are x = 10011001 (-103) and y = 111 (7), the operation is +4x, and the result is m = 412. The simulation results of the radix 8 booth algorithm are depicted in Figure 7, where X and Y are the input multiplicands and m is the

output. As can be seen, two signed binary values are multiplied in the form of their twos complements.

Fig 5: The RTL Schematic of booth algorithm Radix 8

# (b) Simulation Timing Diagram

Fig 6: Simulation Timing Diagram of Booth algorithm Radix 8

#### IV. CONCLUSIONS

The main key parameters for every electronics system are performance and speed. Many low power techniques are being investigated these days to improve performance. The multiplier determines system performance; however the main disadvantage is that it consumes more power and area to improve multiplier performance. Booth algorithm is one of numerous algorithms and types of multipliers accessible. The Booth multiplier have the advantage of having a very high computational speed, which improves the system's performance and speed. We used Xilinx Vivado simulator to implement the Booth algorithms for Radix 4 and Radix 8. We concluded that the Booth algorithm Radix 8 uses less quantity of partial products than Radix 4. As a result, if we design a multiplier employing the booth techniques for radix 8, we can expect very fast computing speed and low power dissipation.

#### REFERENCES

- Najeemulla Baig, Fazal Noorbasha, "CMOS Low Voltage LNA with Improved Noise Figure", International Journal of Innovative Technology and Exploring Engineering (IJITEE), ISSN: 2278-3075, Volume-8 Issue-6, Page No. 606 – 609, April 2019.

- [2]. Najeemulla Baig, Fazal Noorbasha, "Ultra-wide band LNA design using active inductor with modified noise cancellation technique" International Journal of Recent Technology and Engineering (IJRTE) ISSN: 2277-3878, Volume-8 Issue-2, Page No. 2406 – 2410 July 2019.

- [3]. M.Ramkumar Prabhu, A.Rajalingam, J.R.Arunkumar, R.Anusuya, "Microstrip Patch Antenna Using Combined Slots For Bandwidth Enhancement And Size" Journal of Engineering Sciences (JES), Vol 11, Issue 1, Jan / 2020, ISSN NO: 0377-9254.

#### Available at https://jscer.org

- [4]. M.Ramkumar Prabhu, J.R.Arunkumar, A.Rajalingam, R.Anusuya "A Modified Square Patch Antenna with Rhombus slot for High bandwidth" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-9, July 2019.

- [5]. Kiran Kumar Mandrumaka, Fazal Noorbasha, "A low power 10 bit SAR ADC with variable threshold technique for biomedical applications" SN Applied Sciences, (2019) 1:918, https://doi.org/10.1007/s42452-019-0940-3.

- [6]. Kiran Kumar M., Fazal Noorbasha, Rao K.S., "Design of low power 16×16 sram array using GDI logic with dynamic threshold technique" ARPN Journal of Engineering and Applied Sciences, Volume 12, Issue 22, Pages 6571-6576, 1 November 2017.

- [7]. Prathima, C. H., Anusuya, R., & Prabhu, M. R. K. (2022). Comprehensive Design Analysis of Digital Marketing in Agriculture Sector. International Journal of Early Childhood Special Education, 14(5), 2022.

- [8]. Bellamkonda Pragathi , Rajagopal Veramalla, Fazal Noorbasha, Bangarraju Jampana, "Power quality improvement for grid interconnected solar PV system using neural network control algorithm", Int. J. Power and Energy Conversion, Vol. 9, No. 2, Page no. 187 – 204, 2018.

- [9]. Praveen Blessington, Bhaskara B, Fazal Noorbasha, "Estimation of latency and throughput for three-dimensional network-on-chip architecture" Journal of Advanced Research in Dynamical and Control Systems, Volume 10, Issue 7 Special Issue, Pages 1353-1359,2018.

- [10]. Atul Kumar Dwivedi, Deepali Virmani, Anusuya Ramasamy, Purnendu Bikash Acharjee, Mohit Tiwari" Modelling And Analysis Of Artificial Intelligence Approaches In Enhancing The Speech Recognition For Effective Multi-Functional Machine Learning Platform – A Multi Regression Modelling Approach "Journal of Engineering Research - ICMET Special Issue, 2022-04-06.

- [11]. M.Ramkumar Prabhu, A.Rajalingam, J.R.Arunkumar, Dr.R.Anusuya" Microstrip Patch Antenna Using Combined Slots for Bandwidth Enhancement and Size", Journal of Engineering Sciences, Vol 11, Issue 1, Jan, 2020, ISSN NO: 0377-9254.

- [12]. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- [13].Sk.Md.Reyaan, B.Manoj Venkat, G.Y.V.Siva Shankar, K Hari Kishore, Fazal Noorbasha, Y Archana, Shaik Razia "Power Analysis of FIR Filter Design Using APC-OMS Algorithm" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 2, Page No: 1085-1092, March 2020.

- [14]. Anitha A., Rooban S., Sujatha M., 'Implementation of energy efficient gates using adiabatic logic for low power applications', International Journal of Recent Technology and Engineering, 8(3), PP.3327-3332, 2019.

- [15]. Rooban S., Kumar K.S., Shankar K.R., Bhaskara Rao N.U., 'Test and analysis of high performance microprocessor through power binning method', International Journal of Engineering and Advanced Technology, 8(4), PP.882-886,2019.

- [16]. Rooban S., Saifuddin S., Leelamadhuri S., Waajeed S., 'Design of fir filter using wallace tree multiplier with kogge-stone adder', International Journal of Innovative Technology and Exploring Engineering, 8(6), PP.92-96, 2019.

- [17]. Rooban S., Manimegalai R. (2019), 'Prediction of Theoretical Limit for Test Data Compression', Proceedings of the 2018

International Conference on Recent Trends in Advanced Computing, ICRTAC-CPS, PP.41-46, 2018.

- [18].Soumya N., Sai Kumar K., Raghava Rao K., Rooban S., Sampath Kuma R P., Santhosh Kumar G.N.'4-bit multiplier design using cmos gates in electric VLSI', International Journal of Recent Technology and Engineering, 8(2), PP.1172-1177,2019.

- [19].P. Nirmala, T. Manimegalai, J. R. Arunkumar, S. Vimala, G. Vinoth Rajkumar, Raja Raju, "A Mechanism for Detecting the Intruder in the Network through a Stacking Dilated CNN Model", Wireless Communications and Mobile Computing, vol. 2022, Article ID 1955009, 13 pages, 2022. https://doi.org/10.1155/2022/1955009.

- [20].Rooban, S., Swathi, K.L., Monica, C., Shivaramakrishna, B., An odd parity genertor design using nano-electronics ,International Journal of Engineering and Advanced Technology8(4), PP.597-601, 2019.

- [21].Rooban, S., Chowdary, B.N., Vinay, B., Sai Sandeep, M.V.S., 'Design of school bus subscription authentication and management system using face recognition technology, International Journal of Innovative Technology and Exploring Engineering, 8(46), PP.1865-1869,2019.

- [22].Gharabaghlo NS, Khaneshan TM. Performance Analysis of High Speed Radix-4 Booth Encoders in CMOS Technology. Majlesi Journal of Electrical Engineering.;13(3):49-57, 1 Sep 2019.

- [23].Rahnamaei A, Fatin GZ. Circuit Level Realization of Low Latency Radix-4 Booth Scheme for Parallel Multipliers. Proceedings of the National Academy of Sciences, India Section A: Physical Sciences.;92(2):293-301. Jun 2022.